Senior Design Team sample • Sample SD Site

Team Members

Payton Bills

Team LeadDevice Fabrication

I am an Electrical Engineering major starting my concurrent masters program in Fall 2024. I will be specializing in Microelectronics and Photonics and working under Dr. Vikram Dalal on new material solar cells.

Anders Peterson

Device FabricationComponent Design

I am an electrical engineering major and physics minor and will be continuing at ISU to get my MS. My focuses are semiconductor physics and power systems, and I have always been passionate about renewable energy.

Drew Jensen

Fabrication DesignDevice Testing

I am Drew Jensen, a senior in electrical engineering at Iowa State University. I am interested in semiconductors, control systems, and power systems. I wanted to be a part of this project because it is a middle ground between all three of those areas and incorporates many intricacies for all of them. I believe my existing relationship with the people in this group as well as the classes that I've taken, are things that will contribute to our group's success.

Michael Thomas

Fabrication DesignDevice Testing

I am an Electrical Engineering major with three internships completed in Test Engineering, and one internship completed in Electrical Engineer Design. My primary tasks for this project was designing the testing process for our fabricated cells. Because we used an iterative process to designing the fabrication process, this is a key role on the team as we need appropriate data and sample sizes in order to accurately describe what can be improved in the next round of fabrication.

Jonathan Timm

Simulation R&DMaterial Viability

I am a Computer Engineering major with work experience in analog/RF IC design and will be a field application engineering intern at Analog Devices this summer. Simulation software will be used to test various aspects of our manufacturing process and cell design. My programming and simulation experience will support this component of our project. I will also be exploring current solar industry trends to draw conclusions about future economic viability of CdSe.

Jacob Steffens

Simulation R&DMaterial Viability

I am an Electrical Engineering major with a Philosophy minor at Iowa State University. My primary pursuit is VLSI design with an interest in Semiconductor Devices. Most of my course work at ISU has revolved around the use, creation and design of MOSFET based devices. I have a great deal of experience when it comes to testing and verifying Analog and Digital devices. I also have a passion for climbing and sustainability.

Project Overview

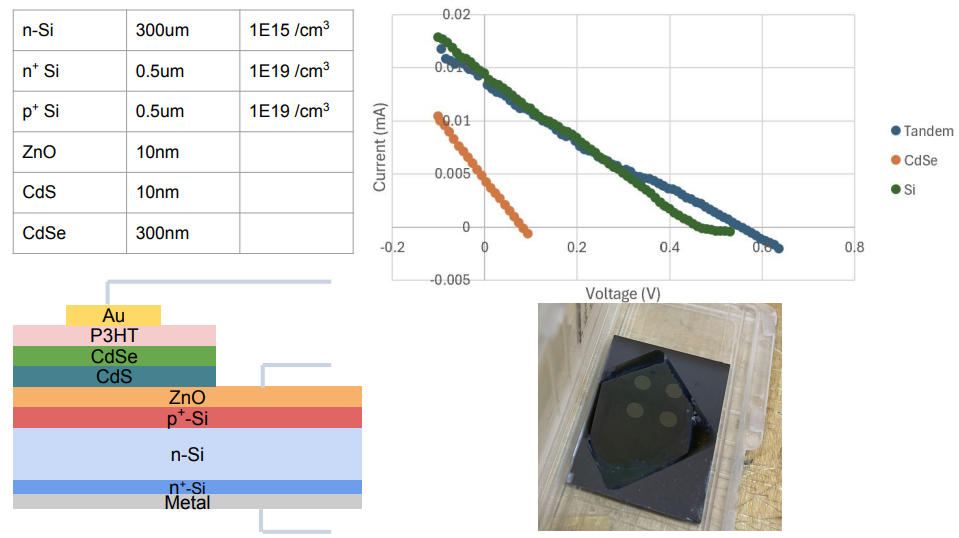

Our project is focused on fabricating a tandem solar cell from Silicon (Si) and Cadmium Selenide (CdSe) as a method of increasing Silicon solar cell efficiency. For tandem cells, there is an ideal energy bandgap match for each material. Ideally, the low energy bandgap should be between 0.9eV and 1.2eV and our higher bandgap should be between 1.7eV and 1.9eV. Since silicon solar cells are already well developed and falls into the low end for ideal efficiency, the idea is to find a material to match it that has a bandgap very similar to silicon's ideal bandgap match, which is 1.7eV. CdSe has a bandgap of 1.74eV and fits the bill nearly perfectly. We are attempting to design and fabricate a Si-CdSe solar that reaches as high an efficiency as possible, with a goal of 1.2Voc. The goal of 1.2Voc comes from previous data in other teams' experiences and from research articles that make us believe this is a realistic goal to achieve.

Project Documents

Spring 2024 Design DocumentFall 2024 Design Document (V2.1)

Demo Video

Final Presentation

Project Poster

Spring 2024 Reports

Report 1Report 2

Report 3

Report 4

Report 5

Report 6

Report 7

Report 8

Report 9

Report 10

Fall 2024 Reports

Report 1Report 2

Report 3

Report 4

Report 5

Lightning Talks

Lightning Talk 1: Problem and UsersLightning Talk 2: User Needs and Requirements

Lightning Talk 3: Project Plan

Lightning Talk 4: Design - Part 1

Lightning Talk 5: Design - Part 2

Lightning Talk 6: Contextualization and Design Check-in

Lightning Talk 7: Ethics